# VIPERLAB

# FULLY CONNECTED **VI**RTUAL AND **P**HYSICAL P**ER**OVSKITE PHOTOVOLTAICS **LAB**

D 8.1

Standardization of substrate dimensions, device layout and best practices

DELIVERABLE

REPORT

Version: 1 Date: 31.05.2022

# DELIVERABLE

# D 8.1 STANDARDIZATION OF SUBSTRATE DIMENSIONS, DEVICE LAYOUT AND BEST PRACTICES

#### **Project References**

| Project Acronym            | VIPERLAB                                                                                 |

|----------------------------|------------------------------------------------------------------------------------------|

| Project Title              | Fully connected <b>vi</b> rtual and physical <b>per</b> ovskite photovoltaics <b>lab</b> |

| Project Coordinator        | Helmholtz-Zentrum Berlin                                                                 |

| Project Start and Duration | 1st June 2021, 42 months                                                                 |

#### **Deliverable References**

| Deliverable No          | D 8.1                                                                                |

|-------------------------|--------------------------------------------------------------------------------------|

| Туре                    | Report                                                                               |

| Dissemination level     | Confidential, only for members of the consortium (including the Commission Services) |

| Work Package            | WP8                                                                                  |

| Lead beneficiary        | Swansea University (SU)                                                              |

| Due date of deliverable | 31 May 2022                                                                          |

| Actual submission date  | 31 May 2022                                                                          |

| Version | Status        | Date       | Beneficiary | Author                     |

|---------|---------------|------------|-------------|----------------------------|

| 1.0     | First Draft   | 10.05.2022 | SU          | R. Patidar                 |

| 1.1     | Revised Draft | 24.05.2022 | SU / TNO    | R. Patidar /<br>S.Veenstra |

| 1.2     | Review        | 30.05.2022 | HZB         | N. Maticiuc                |

VIPERLAB D8.1 Standardization of substrate dimensions, device layout and best practices

#### DISCLAIMER

'Fully connected virtual and physical perovskite photovoltaics lab' VIPERLAB is a Collaborative Project funded by the European Commission under Horizon 2020. Contract: 101006715, Start date of Contract: 01/06/2021; Duration: 42 months.

The authors are solely responsible for this information, and it does not represent the opinion of the European Community. The European Community is not responsible for any use that might be made of the data appearing therein.

VIPERLAB D8.1 Standardization of substrate dimensions, device layout and best practices

3 / 10

## TABLE OF CONTENTS

| 1. | EX   | (ECUTIVE SUMMARY                              | .4 |

|----|------|-----------------------------------------------|----|

| 2. | IN.  | TRODUCTION                                    | .4 |

|    | 2.1. | SUBSTRATE SIZE                                | .4 |

|    | 2.2. | PATTERNING TRANSPARENT CONDUCTIVE OXIDE (TCO) | .5 |

|    | 2.3. | MEASURED ACTIVE AREA                          | .6 |

|    | 2.4. | TOP CONTACT                                   | .6 |

|    | 2.5. | ENCAPSULATION                                 | .7 |

| 3. | GE   | ENERIC DESIGNS                                | .8 |

| 4. | СС   | ONCLUSION                                     | .9 |

| 5. | BI   | BLIOGRAPHY                                    | .9 |

#### 1. EXECUTIVE SUMMARY

VIPERLAB is a collaborative project that fosters collaboration between academia and industry while also facilitating and coordinating access to the most advanced EU-based perovskite research infrastructures. Towards this larger goal, through WP8, this deliverable aims to deliver a standardized architecture for device fabrication to enable seamless sample sharing. We will be laying out some factors and guidelines considered for the standardization of device design which is then evaluated to propose a standard design. To this end, we will compare these factors with the design data we gathered from the VIPERLAB partners and from the perovskite database to propose a design that is easy to adopt by research groups without needing to modify many processes.

#### 2. INTRODUCTION

Traditionally every research group within the community has been designing their device architecture. The choice of designs is largely subjective but also depends on some technical and scientific reasons. For the efficient movement of the samples between the collaborators, it is necessary to standardize some of these subjective choices while also considering the efficient use of materials and time to get maximum data sets from one substrate. The literature is sparsely filled with information about design factors that can affect design choices. We have taken the initiative to list factors we considered for the generic design.

- 1. Substrate Size

- 2. Transparent Conductive Oxide Pattern

- 3. Measured Active Area

- 4. Top Contact and Masking1

- 5. Encapsulation

#### 2.1. Substrate Size

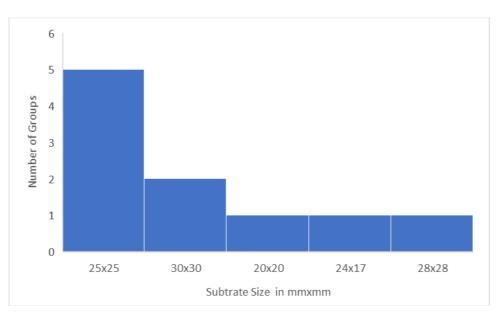

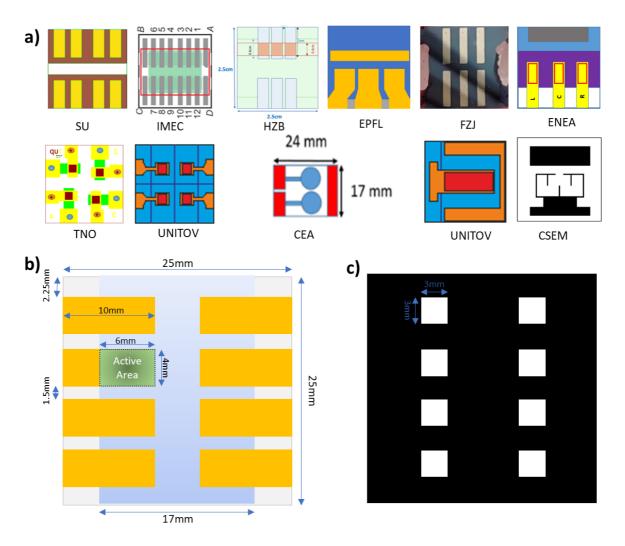

Substrate size can vary greatly between groups, all the way from <1cm<sup>2</sup> to 3 or 4 cm<sup>2</sup> for small-scale experiments. It is therefore a difficult task to propose a standard size since this could depend on the respective group's capability to handle varied sizes. To our understanding, no literature supports or refutes the idea that the size of the substrate has any relationship to the performance and efficiency of PSCs. However, it is to be noted that we are referring specifically to substrate size and not active/device area. Active area can have an impact on the device's performance. To choose a standard size we sorted the data we collected from the VIPERLAB partners. As can be seen in Figure 1 majority of the groups uses 25x25 mm<sup>2</sup> as the standard size to make the transition easy for as many as possible.

Figure 1. Different substrate sizes used by VIPERLAB partners

### 2.2. Patterning Transparent Conductive Oxide (TCO)

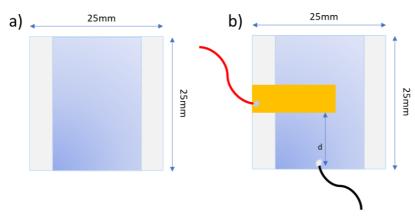

TCO is commonly used as the bottom electrode for perovskite solar cells (PSCs). It is patterned (removing TCO from some part of the substrate) so that two (bottom and top) contacts can be separated to avoid any risk of shorting the device while making an external contact for the measurement. There are many ways to pattern the TCOs. Again, we did not find any available research to ascertain a relationship if any between TCOs patterns and the performance of PSCs. However, we need to be mindful of the conductivity of the TCOs. If poorly conducting TCO is used it is vital to keep the distance between the active device area and external contact (distance 'd' as shown in Figure 2b) low to avoid resistive losses. This concept would also apply to top contact but generally for high-efficiency devices highly conductive metal contacts are used. Taking this into the account, the simplest design would be to etch TCO from the sides of the substrates and design the top contact such that it contacts the non-TCO part (Figure 4b) which then can be used to make the external connections. We show a plausible design for this in Figure 2a.

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement N°101006715

6 / 10

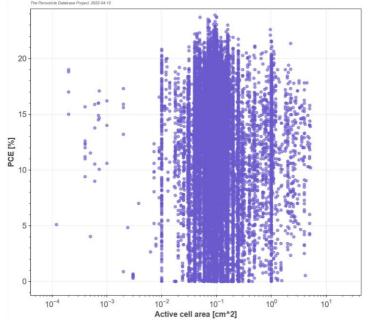

#### 2.3. Measured Active Area

It is essential to identify the active area before designing the top contact patterns. Unlike other factors discussed so far, active areas do have an impact on the measured performance of PSCs. The extent of this effect depends on the conductivity of the TCO, the uniformity of the coatings, and the conductivity of top contact as well. To get a perspective on the most widely used active area reported for the measurement, we took the data from the perovskitedatabase.com<sup>1</sup> of various active area devices the community has published in peer-reviewed journals, and the resultant image is shown in Figure 3. As can be interpreted from the figure, most of these reported results are with active areas in the region of 0.1 cm<sup>2</sup>. Hence for the wide and easy adoption of the proposed architecture, we propose the active area for current-voltage measurement to be in the range of 0.1 cm<sup>2</sup>. And all our further designing will be done considering this value.

Figure 3. Performance vs Active Area from the perovskite database.<sup>1</sup>

# 2.4. Top Contact

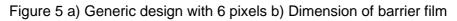

For the design of the top contact, two things must be kept in check. First, the top contact should not be too big than the active/device area to be measured (0.09cm<sup>2</sup> in our case) as this may lead to compromised data.<sup>2</sup> Second, to check the uniformity across the substrate and to get the maximum data points from the single substrate, the design of the top contact must be such that multiple devices can be measured on a single substrate across the area. Figure 4a shows the different kinds of designs used by VIPERLAB consortium members. One pattern stands out of all these different designs as used by the majority groups, the 'finger-like' pattern. The finger-like pattern is when the top contact is evaporated on opposite edges or one side of the substrate orthogonal to the TCO pattern in a rectangular-shaped bar. The bars must have enough length to contact the non-TCO component, which is then connected to an external contact. Each bar/finger represents an individual

device. Thus, to cover the whole substrate and get maximum devices on it we put 4 devices on each side leaving enough gap in between devices as shown in Figure 4b. We further designed the mask for masking the device to 0.09cm<sup>2</sup> for the measurement. (Figure 4c).

Figure 4. a) All the designs collected from the VIPELAB members; b) Proposed generic design; c) Photo mask for measurement for the design in shown in b).

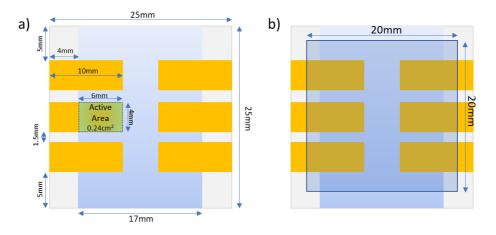

# 2.5. Encapsulation

PSCs are highly sensitive to external conditions, so it is crucial to encapsulate them to preserve their original performance and properties. This is particularly important when shipping samples across the globe to collaborators. Encapsulation does affect the design choices. Encapsulation can be done in two ways, glass-glass encapsulation (PET-PET in case of flexible PSCs or with any barrier films) or coating/printing a barrier layer on top of the PSCs. To enable measurement after encapsulation, a small gap must be left at the edges of the substrates exposing the top and bottom electrodes to allow

for connection to external contacts. This can be achieved by using a barrier film of a smaller size than the substrate. However, the design proposed in Figure 4b does not have enough space for a barrier film that is covering all the pixels and leaves enough space exposed to make external contact. To solve this, we went from an 8-pixel design to a 6-pixel design. This leaves us with a gap of 5mm on the y axis and 4mm on the x axis from the active area shown in Figure 5a. For encapsulation, a barrier film of 20mmx20mm leaves a decent 2.5mm of gaps on all sides for external contacts connection as shown in Figure 5b.

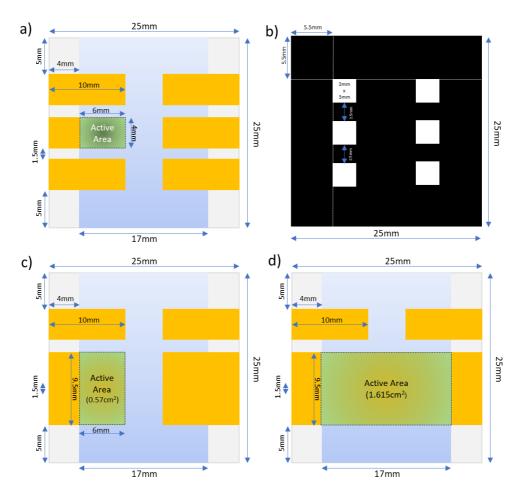

#### 3. GENERIC DESIGNS

We considered 5 factors and created a generic design that would be sufficient for most cases. This design can be used to measure active surfaces up to 0.24cm<sup>2</sup>. In figure 5c we show the schematic representation of a mask for the measurement of 0.09cm<sup>2</sup> active area. In some cases, however, we may need the measurement for a larger area. For this to be done without having to change the testing setups a modified design is built on top of the generic design. This can be achieved by merging devices horizontally or vertically. By merging two pixels vertically we can get an active area of up to 0.57cm<sup>2</sup> as shown in Figure 6c. This area can be further increased to 1.6cm<sup>2</sup> by merging 4 pixels horizontally as shown in Figure 6d. All this is done while always having a smaller pixel (<0.24cm<sup>2</sup>) in the design which can act as a control measurement.

Figure 6 a) Proposed generic design with active area up to 0.25 cm<sup>2</sup>. b) Photo mask for the generic design. c) 4-pixel design with active area up to 0.57cm<sup>2</sup>. d) 3-pixel design with active area up to 1.6cm<sup>2</sup>.

#### 4. CONCLUSION

By taking a bottom-up approach we proposed a generic design by considering the current device architecture used by the members of VIPERLAB and factors like maximum data extraction, low resistive losses, and most used designs for an easy transition to the generic design. This will help the effortless exchange of samples across the labs and would further promote collaboration. WP4 will host workshops and other events to disseminate the harmonised design and procedures. This design will also be communicated to the community via WP4.

# 5. BIBLIOGRAPHY

- 1. Jacobsson, T. J. *et al.* An open-access database and analysis tool for perovskite solar cells based on the FAIR data principles. *Nature Energy 2021 7:1* **7**, 107–115 (2021).

- 2. Kiermasch, D., Gil-Escrig, L., Bolink, H. J. & Tvingstedt, K. Effects of Masking on Open-Circuit Voltage and Fill Factor in Solar Cells. *Joule* **3**, 16–26 (2019).

VIPERLAB D8.1 Standardization of substrate dimensions, device layout and best practices

10 / 10